2016年8月 Journal of Terahertz Science and Electronic Information Technology

Aug., 2016

文章编号: 2095-4980(2016)04-0606-04

# 基于晶振倍频鉴相的 C 波段低相噪频率源设计

董洪新, 邰战雄, 李 强, 杨 洋, 朱中浩, 宋烨曦

(四川九洲电器集团有限责任公司,四川 绵阳 621000)

摘 要: 针对数字锁相技术相位噪声的构成和特性进行了探讨与研究,并在对比传统单环锁相方案的基础上,介绍了一种基于晶振倍频信号作为参考进行鉴相的低相噪频率合成器。经测试,传统锁相方案在输出 6 480 MHz 时,相位噪声为 -109.1 dB/Hz@10 kHz。而本文设计的低相噪频率源在使用同样的参考晶振、锁相环芯片以及压控振荡器的情况下,输出相同频率时,相位噪声相比传统方案改善了约 8 dB。

关键词: 低相位噪声; 倍频; 锁相环

中图分类号:TN74

文献标识码:A

doi: 10.11805/TKYDA201604.0606

# Design of a C-band low phase noise frequency synthesizer based on phase detecting with crystal oscillator multiplication

DONG Hongxin, TAI Zhanxiong, LI Qiang, YANG Yang, ZHU Zhonghao, SONG Yexi (Sichuan Jiuzhou Electric Group Co., Ltd., Mianyang Sichuan 621000, China)

**Abstract:** The phase noise composition and characteristics of a digital Phase Locked Loop(PLL) are investigated. A phase locked frequency synthesizer based on crystal oscillator multiplication is presented. Compared with the traditional frequency synthesizer based on single PLL, the proposed design achieves lower phase noise. According to the test results, the phase noise of -109.1 dB/Hz@10 kHz is achieved by the traditional approach when the output is 6 480 MHz; while a better phase noise performance of -117 dB/Hz@10 kHz is reached by the proposed design at the same frequency, using the same crystal oscillator PLL chip and Voltage Controlled Oscillato(VCO), which is improved by 8 dB compared to the traditional design.

Key words: low phase noise; frequency multiplication; Phase Locked Loop

随着现代无线通信和雷达技术的快速发展,通信系统和雷达系统的性能面临着更高也更严苛的挑战,频率源作为系统的关键部件之一,将直接影响系统的整体性能。相位噪声是频率合成技术的关键指标<sup>[1]</sup>,直接决定无线系统和雷达系统的通信质量和检测精确度等<sup>[2-3]</sup>。本文采用晶振倍频作为参考信号的方法对传统锁相环技术进行改进,使得相位噪声指标得到一定程度优化,在高频率低相噪的应用领域具有较大的优势。

#### 1 锁相环的相位噪声特性

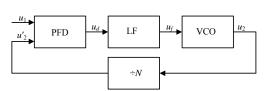

锁相环可以被视为一个针对相位的控制系统,它作用于压控振荡器(VCO),使得信号 $u'_2$ 的频率与信号 $u_1$ 的频率保持一致,而信号 $u'_2$ 的相位与信号 $u_1$ 的相位几乎相等或者与后者有一个常数偏差,即压控振荡器输出信号的相位与参考信号的相位相互锁定<sup>[4]</sup>。图1显示了一个简单的锁相环结构图。

锁相环的相位噪声主要分为环内和环外2部分,其中环外相位噪声主要由VCO决定,而环内相位噪声主要受鉴相器噪声基底的影响<sup>[5]</sup>,通常所关注的相位噪声主要是指环内相位噪声,其计算方法如下。

Fig.1 Diagram of a phase locked frequency synthesizer 图 1 锁相式频率合成器结构图

基底相位噪声计算方法[6]:

$$PN_{\text{floor}} = \text{FOM} + 10\log(f_{\text{pd}}) + 20\log(f_{\text{vco}}/f_{\text{pd}}) = \text{FOM} - 10\log(f_{\text{pd}}) + 20\log(f_{\text{vco}})$$

(1)

式中:FOM为鉴相器归一化基底噪声; $f_{pd}$ 为锁相环鉴相频率; $f_{vco}$ 为锁相环输出频率。

## 2 C 波段低相噪频率合成器工作原理

在一般的锁相环电路设计当中,往往直接采用晶振的输出信号作为锁相环的参考,而晶振具有的高稳定高纯度特性决定了其归一化相位噪声远远优于鉴相器的归一化噪声基底,因此在计算锁相环输出信号的相位噪声时,往往忽略晶振的影响。即在一般的锁相环设计中,晶振的低相位噪声特性并没有得到完全的利用和发挥。基于这个原因,本文设计了一种锁相环结构,充分利用晶振的低相位噪声特性,使最终的相位噪声优于相同频率下由传统锁相环得到的相位噪声。

当参考信号的相位噪声特性接近或劣于鉴相器的噪声特性时,输出信号的相位噪声特性除了鉴相器的噪声外还需要加上晶振的影响。此时,相位噪声由式(2)得到<sup>[7]</sup>:

$$PN = 10\log\left(10^{\frac{PN_{\text{floor}}}{10}} + 10^{\frac{PN_{\text{ref}}}{10}}\right)$$

(2)

式中:  $PN_{\text{ref}} = PN_{\text{cry}} + 20\log(f_{\text{vco}}/f_{\text{pd}})$ ;  $PN_{\text{cry}}$ 为晶振相位噪声。

式(2)处于对数坐标系中,若 PN<sub>ref</sub> 相对 PN<sub>floor</sub>大 3 dB 以上时,则鉴相器对信号的影响往往可以忽略。在这种情况下,输出信号的相位噪声可视为参考信号相位噪声倍频恶化而来,从而实现理论上的相位噪声最优化。

# 3 电路的设计和实现

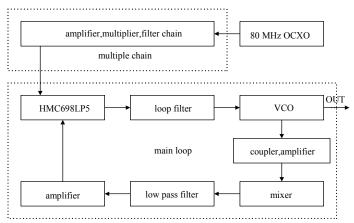

本文研究的 C 波段低相噪频率合成器由 2 部分组成:分别为 OCXO 倍频电路和锁相环电路。晶振给出的信号经多次放大倍频滤波得到满足要求的高频参考信号,而后在锁相环电

Fig.2 Diagram of the C-band frequency synthesizer with low phase noise 图 2 C 波段低相噪频率合成器原理框图

路中与 VCO 输出信号相位锁定,从而得到期望的输出信号。

本文设计的低相噪频率综合器技术指标如下:输出频率: 6 480 MHz;相位噪声:  $\leq$ -115 dB/Hz@10 kHz; 频率稳定度:  $\leq$ 1×10<sup>17</sup>;杂散抑制:  $\leq$ -70 dB; 谐波抑制:  $\leq$ -50 dB;输出功率:  $\geq$ 0 dBm。

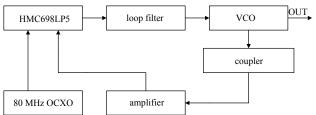

通过对指标分析,可以看出该频率源的设计难点在于需要在较高的输出频率下满足较低的相位噪声指标。根据上述指标要求本文设计了图2原理框图所示的低相噪频率合成器。作为对比,本文同时设计了一款基于传统单环锁相技术的频率合成器,原理框图如图3所示。

在该工程实例中,采用 AXTAL 公司的低相噪系列恒温晶振为整个系统提供基准信号,

Fig.3 Diagram of the frequency synthesizer with the traditional single PLL 图 3 传统单环方案频率合成器原理框图

保证系统的低相噪指标得以实现,该晶振的相位噪声为  $-159\,\mathrm{dBc}/\mathrm{Hz}$  @  $10\,\mathrm{kHz}$  。倍频链电路将晶振 80 MHz 基准信号 9 倍频到 720 MHz 作为主环电路的参考信号。由式(1)可以看出,通过提高锁相环的鉴相频率  $f_{\mathrm{pd}}$  可以减小  $PN_{\mathrm{floor}}$  ,但  $PN_{\mathrm{ref}}$  会增大,当 2 项达到平衡时,PN 则可达到最优值。利用倍频链将参考信号的相位噪声提高到鉴相器基底相位噪声之上,以使得晶振的低相噪特性得到充分利用,提高整个模块的相噪特性。

主环电路选用 HITTITE MICROWAVE 公司设计的 VCO 芯片 HMC466LP4, 其输出频率范围为 6.1 GHz~

6.72 GHz, 符合指标要求。主环电路的核心芯片采用了该公司设计的高鉴相频率数字锁相环芯片 HMC698LP5。 该芯片拥有较低的基底噪声,参考信号频率最高可达 1 300 MHz,反馈射频信号频率高达 7 GHz,满足本次设计 的特殊要求。本次设计中,鉴相频率为720 MHz,反馈信号分频比为9。

采用式(2)对本文所设计的 C 波段低相噪频率合成器的相位噪声进行计算, 计算结果如下:

$$PN_{\text{floor}} = -230 + 10 \lg 720 \times 10^6 + 20 \lg 9 = -125.3 \, \text{dB / Hz}$$

(3)

$$PN_{ref} = -159 + 20 \lg 81 = -120.8 \, dB / Hz @ 10 \, kHz$$

(4)

因此,

$$PN = 10 \lg \left( 10^{\frac{-125.3}{10}} + 10^{\frac{-120.8}{10}} \right) = -119.4 \, dB / Hz @ 10 \, kHz$$

(5)

传统锁相环电路如图 3 所示。恒温晶振的信号直接为锁相环芯片 HMC698LP5 提供参考信号,鉴相频率为 80 MHz, 反馈信号分频比为81。利用式(1)对偏离载波10 kHz的相位噪声进行计算:

$$PN = PN_{\text{floor}} = -230 + 10 \log 80 \times 10^6 + 20 \log 81 = -112.8 \text{ dB} / \text{Hz} @ 10 \text{ kHz}$$

(6)

从上述的理论计算结果可以看到,本文所设计的 C 波段低相噪频率合成器相对于传统的单环锁相方式在同 样的晶振、锁相环芯片以及 VCO 芯片基础上,相位噪声指标可以得到约 7 dB 的改善。

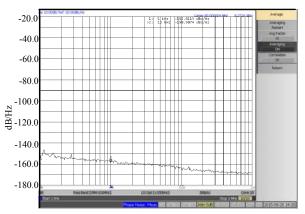

Fig.4 Phase noise test results of the 80 MHz crystal oscillator 图 480 MHz 晶振相噪测试结果

Fig.5 Phase noise test results of the 720 MHz multifrequency chain 图 5 720 MHz 倍频链相噪测试结果

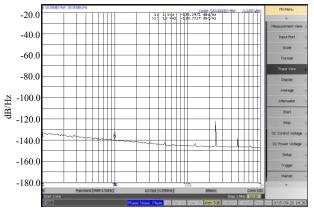

frequency synthesizer

图 6 C 波段低相噪频率合成器相噪测试结果

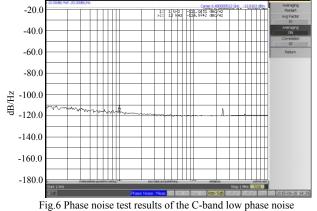

Fig.7 Phase noise test results of the frequency synthesizer with the traditional signal PLL

图 7 传统单环方案频率合成器相噪测试结果

#### 测试结果及指标分析

本文采用Agilent公司设计的E5052B信号源分析仪对合成器的指标进行测量。图4的测试结果显示AXTAL公司 提供的晶振的相噪指标为-159.0 dB/Hz@10 kHz; 经过倍频后相噪指标将按照 20log N 的规律恶化<sup>[8]</sup>, 得到 720 MHz主环参考信号的理论相噪应为-159+20lg9=-139.9 dB/Hz@10 kHz。图5显示倍频链电路的输出信号相噪

指标为-139.7 dB/Hz@10 kHz,表明本文设计的倍频链电路几乎没有引入额外的噪声干扰恶化系统相噪指标。 图6和图7的测试结果得到本文设计的C波段低相噪频率合成器相比传统单环锁相方案相位噪声指标改善约8 dB。其中C波段低相噪频率合成器相位噪声测试结果为-117.0 dB/Hz@10 kHz,作为对照系的传统方案相位噪声为-109.1 dB/Hz@10 kHz。该测试结果与前文的理论计算值相比有2 dB~3 dB的恶化,因为理论计算为理想状态,所以该测量值在允许的误差范围内。

## 5 结论

本文利用倍频链将晶振的低相噪信号倍频,将参考信号的相位噪声恶化到与鉴相器基底噪声相当或更差的程度,使得晶振带来的相位噪声在合成器的输出当中所占比重与鉴相器所带来的相位噪声比重相当或更大,从而使晶振的低相位噪声特性得到完全的利用和发挥。相比传统的单环锁相方案,系统的相位噪声特性在相同的器件基础上大大改善。在高频率低相噪的频率源应用领域具有较大的优势以及广阔的应用前景。

#### 参考文献:

- [1] 白居宪. 低噪声频率合成[M]. 西安:西安交通大学出版社, 1995. (BAI Juxian. Low Noise Frequency Synthesizer[M]. Xi'an, China:Xi'an Jiaotong University Press, 1995.)

- [2] 丁鹭飞,耿富录,陈建春. 雷达原理[M]. 北京:电子工业出版社, 2013. (DING Lufei,GENG Fulu,CHEN Jianchun. Radar Principles[M]. Beijing:Publishing House of Electronics Industry, 2013.)

- [3] 张光义,赵玉洁. 相控阵雷达技术[M]. 北京:电子工业出版社, 2006. (ZHANG Guangyi,ZHAO Yujie. Phased Array Radar Technology[M]. Beijing:Publishing House of Electronics Industry, 2006.)

- [4] ROLAND Dr E Best. Phase Locked Loops:Design, Simulation, and Applications [M]. 6th ed. New York:McGraw-Hill Professional, 2007

- [5] VADIM Manassewitsch. Frequency Synthesizers: Theory and Design[M]. 2nd ed. Hoboken: Wiley-Interscience, 1980.

- [6] WILLIAM F Egan. Phase-Lock Basics[M]. 2nd ed. Hoboken:Wiley-IEEE Press, November, 2007.

- [7] 杨超越. 微波多频段高品质本振源研究[M]. 成都:电子科技大学出版社, 2013. (YANG Chaoyue. Study of Microwave Multiband of High Quality Local Oscillator[M]. Chengdu, China: Press of UESTC, 2013.)

- [8] 高树亭,高峰,徐盛旺,等. 合成频率源工程分析与设计[M]. 北京:兵器工业出版社, 2008. (GAO Shuting,GAO Feng,XU Shengwang,et al. The Design and Analysis of Synthesized Frequency Source[M]. Beijing:The Publishing House of Ordnance Industry, 2008.)

#### 作者简介:

董洪新(1976-), 男, 江苏省扬州市人, 学士, 研究方向为射频接收技术及相关产品. email:284608529@qq.com.

**杨 洋**(1982-),男,四川省新津县人,学士,工程师,研究方向为发射机模块及相关产品.

部战雄(1978-),男,山西省临汾市人,学士,工程师,研究方向为微波射频放大电路及相关产品.

李 强(1978-),男,四川省邻水县人,学士, 工程师,研究方向为接收机及相关产品.

朱中浩(1988-),男,四川省达州市人,硕士,助理工程师,主要研究方向为频率合成器及相关产品.

宋烨曦(1985-),男,四川省乐山市人,硕士, 工程师,研究方向为频率合成器及相关产品.