Journal of Terahertz Science and Electronic Information Technology

Vol. 16, No. 6 Dec., 2018

文章编号: 2095-4980(2018)06-1109-04

# 用于星光 III 激光同步系统的低抖动时钟整形技术

刘亚迪 1,2, 王 超 1, 党 钊\*1, 陈 骥 1

(1.中国工程物理研究院 激光聚变研究中心,四川 绵阳 621999; 2.东南大学 生物科学与医学工程学院,江苏 南京 210096)

摘 要: 针对参考时钟源高电平脉冲宽度窄(小于2 ns)和本底噪声大的问题,通过使用一种时钟低抖动整形技术方案,使参考时钟经过锁相整形后高电平脉冲宽度大于3 ns、锁相相位时间抖动均方根(RMS)值小于5 ps。目前该方案已成功用于星光III激光装置的联机实验,情况良好,对其他类似需要精密时钟的装置具有极大的借鉴意义。

关键词:脉冲宽度;本底噪声;低抖动;时钟整形;信号完整性

中图分类号: TN249

文献标志码:A

doi: 10.11805/TKYDA201806.1109

# A low jitter clock reshaping technology for XG-III laser system

LIU Yadi<sup>1,2</sup>, WANG Chao<sup>1</sup>, DANG Zhao<sup>\*1</sup>, CHEN Ji<sup>1</sup>

(1.Research Center of Laser Fusion, China Academy of Engineering Physics, Mianyang Sichuan 621999, China; 2.Department of Biomedical Engineering, Southeast University, Nanjing Jiangsu 210096, China)

Abstract: A low jitter clock shaping scheme is proposed, which solves the problem of high pulse with narrow width(less than 2 ns) and large noise floor of the reference clock source. The technical specifications achieved are the high reference clock pulse width greater than 3 ns, phase-locked phase jitter Root Mean Square(RMS) less than 5 ps after Phase Locked Loop(PLL). And the signal integrity simulation design verification is further realized through the Input/Output Buffer Information Specification (IBIS) model. At present, the scheme has been successfully used in online experiment of XG-III laser device and is in good condition. It is of great reference to the accurate implementation of the synchronization system of radiation sources in different frequency bands.

Keywords: pulse width; noise floor; low jitter; clock reshaping; signal and power integrity

星光 III 激光装置同步系统提供的同步触发信号,要求与输出功率 100 TW 的激光装置 74.55 MHz 振荡器精密同步<sup>[1]</sup>,时间抖动均方根值(RMS)小于 10 ps。为了保证高精确度的时间同步,星光 III 激光装置同步系统的参考时钟源为 100 TW 激光装置振荡器输出的 74.55 MHz 飞秒级光脉冲信号,该光脉冲信号经过光电转换、锁相倍频后作为星光 III 同步系统的工作时钟<sup>[2]</sup>。采用该技术方案完成星光 III 同步系统的研制,在实际应用中,最初一段时间内同步触发时序稳定,但是经过一段时间后,发现同步触发信号存在时间漂移的情况,且时间漂移达到 2 ns 左右;偶然还发生同步触发信号的工作频率异常,同步信号频率增加了一倍。因此本文对同步时序频率异常以及时间漂移问题进行分析,并提出一种时钟低抖动整形方案。

# 1 低抖动时钟整形技术方案

# 1.1 星光 III 同步时序异常原因分析

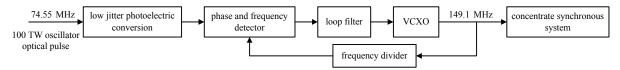

星光 III 同步系统工作时钟见图 1,74.55 MHz 飞秒级光脉冲信号经过光电转换、锁相倍频作为星光 III 同步系统工作时钟,但在应用过程中出现了同步时序异常的情况。

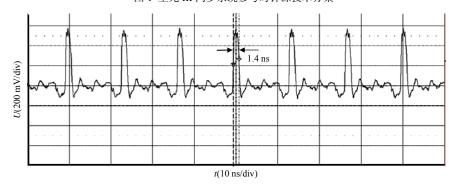

对同步时序信号频率异常时的现场进行测试,见图 2,发现 100 TW 激光装置振荡器产生的 74.55 MHz 飞秒级脉宽光脉冲经过光电转换后的时序信号的底部噪声太大,脉冲过冲与振荡严重,导致后续锁相环电路将噪声作为参考频率信号,引起同步系统输出时序的异常<sup>[3-4]</sup>。

收稿日期: 2017-11-22; 修回日期: 2018-02-08

\*通信作者: 党 钊 email:qingzhaodangma@caep.cn

Fig.1 Design of reference clock source in XG-III synchronous system 图 1 星光 III 同步系统参考时钟源技术方案

Fig.2 Original signal of the optical pulse output from 100 TW oscillator after photovoltaic conversion 图 2 100 TW 振荡器输出的光脉冲光电转换后的原始信号

针对同步触发信号存在的时间漂移情况,开展了现场实验测试及监控,最初几次未发现异常情况,见图 2,偶然发现光电探测器的角度轻微变化,100 TW 激光装置振荡器产生的 74.55 MHz 飞秒级脉宽光脉冲经过光电转换后的高电平电脉冲宽度也在变化,高电平脉冲宽度在 1.4~2.1 ns 之间变化,当高电平脉冲宽度大于 2 ns 时,同步系统同步时序正常;当高电平脉冲宽度小于 2 ns 时,同步系统同步时序存在漂移,漂移时间范围在 2 ns 内。因此,参考时钟的高电平脉冲宽度必须大于 2 ns 才能保证锁相环稳定可靠工作。针对同步系统时钟源信号底部噪声大,高电平脉冲宽度窄且脉冲宽度不稳定的情况,本文提出了一种低抖动时钟整形技术方案。

#### 1.2 低抖动时钟整形技术方案

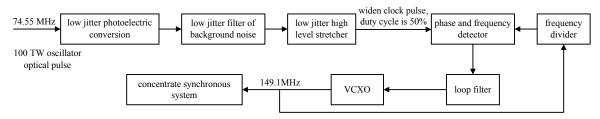

为了保证星光 III 激光装置同步系统的参考时钟源为 100 TW 激光装置振荡器输出的 74.55 MHz 飞秒级光脉冲信号,该光脉冲信号经过光电转换、锁相倍频后作为星光 III 同步系统的工作时钟<sup>[2]</sup>。低抖动时钟整形技术方案见图 3,100 TW 激光装置振荡器输出的 74.55 MHz 光脉冲光电转换后,再经过高速比较电路进行整形滤波,通过高速比较阈值的精确调整,滤除时钟源信号的底部振荡噪声<sup>[5]</sup>。

Fig.3 Design of low jitter clock reshaping 图 3 抖动时钟整形技术方案

针对时钟源信号高电平较窄的问题,采用时钟触发 GHz 以上工作频率的高速触发器工作,该类触发器在时钟信号的上升沿实现一次状态翻转,两次翻转完成一次脉冲信号输出,从而实现占空比 50%的精密时钟信号的输出。采用该类脉冲占空比提升技术,输出时钟信号的高电平宽度得到展宽,但时钟信号的工作频率为原时钟源信号频率的二分之一,因此在后级采用精密锁相环技术实现时钟信号的精密倍频输出<sup>[6]</sup>。

#### 2 关键技术研究及实验验证

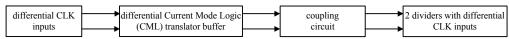

根据时钟低抖动整形技术方案,完成如图 4 所示的关键电路研制。该电路采用带时钟差分输入高速比较的时钟分配电路,实现时钟源信号底部振荡噪声的滤波;采用 GHz 低抖动二分频电路,实现时钟占空比的高速低抖动展宽,从而实现时钟信号高电平部分的低抖动展宽,解决参考时钟高电平脉冲宽度窄,本底噪声大的问题。

Fig.4 Significant circuit of low jitter clock reshaping system 图 4 时钟低抖动整形关键电路

在电路的 PCB 设计中,进行了信号的完整性设计及仿真<sup>[7]</sup>。信号完整性是指在高速产品中由互连线的电气特性对数字波形造成的不同影响,包括振铃、反射、近端串扰、开关噪声等问题。对关键网络进行仿真,可以在制作硬件之前对系统性能进行预测,以精确预测信号完整性效应<sup>[8]</sup>。本电路为高速电路设计,进行信号完整性、阻抗匹配的仿真设计很有必要<sup>[6]</sup>。其中有源器件常用的模型有集成电路仿真程序(Simulation Program with Integrated Circuit Emphasis,SPICE)模型和输入/输出缓冲器信息规范(IBIS)模型。SPICE 模型要用到理想源和无源器件的组合,或基于晶体管几何结构的专用晶体管模型,其包含了驱动器的具体特征与工艺技术的有关信息,大多数厂商不愿意给出芯片的 SPICE 模型。而 IBIS 是一个行为模型,通过 V/I 和 V/T 数据描述器件数字输入和输出的电气特性,可以不泄露晶体管几何结构的技术产权信息,比较容易获得。因此选用 IBIS 模型进行信号完整性仿真设计,能够预测出连接不同器件的传输线路中基本的信号完整性问题,如反射、串扰、接地和电源反弹、过冲、欠冲等<sup>[9]</sup>。

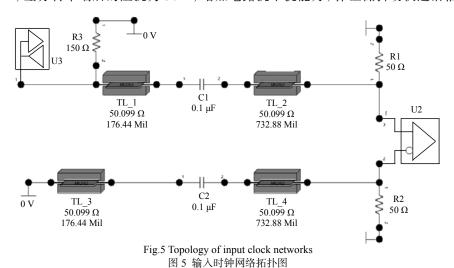

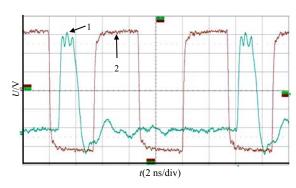

本设计采用 IBIS 模型进行信号完整性仿真设计,图 5 为输入脉冲网络拓扑图,图 6 为对应的仿真波形图,其中线 1 输入信号,线 2 为经过拓扑网络进入芯片的输入差分信号,满足差分信号幅度大于 200 mV 的要求,波形质量较好,没有发生比较大的反射等信号完整性问题。同时采用差分对走线并对信号线做阻抗匹配设计: 差分线对的阻抗为  $100 \Omega$ ,差分转单端后的阻抗为  $50 \Omega$ ,增加电路抗干扰能力,保证低抖动快边沿信号的非失真传输。

1.25 V 2 1.25 V 30 40 50 60 70 80 90 100 110

Fig.7 Experiment result of synchronous system 图 7 同步系统联机实验验证测试

经过整形滤波、展宽、锁相倍频后时钟信号与同步信号联机实验验证的测试情况见图 7, 曲线 1 为 77.45 MHz 飞秒级激光脉冲信号, 曲线 2 为经过整形滤波、展宽、锁相倍频输出的信号, 频率为 149.1 MHz, 时钟信号底部干净、时钟占空比 50%、高电平脉冲宽度大于 3 ns, 与参考时钟源的时间抖动小于 5 ps(RMS), 满足应用要求, 并解决了同步时序异常的问题。

### 3 结论

本文提出了一种时钟低抖动整形技术方案,该方案采用高速比较电路实现低抖动滤波;采用高速时钟触发器电路实现时钟高电平脉冲低抖动展宽,锁相整形后参考时钟的高电平脉冲宽度大于 2 ns;采用精密锁相环技术实现时钟信号频率提升,锁相相位时间抖动小于 5 ps(RMS),解决了 100 TW 振荡器提供的参考时钟源的高电平脉冲宽度窄(2 ns 左右)、本底噪声大的问题。并通过 IBIS 模型进行了信号完整性分析及验证。目前该技术方案已经成功地用于星光 III 激光装置的联机实验,情况良好,该低抖动时钟整形技术对其他类似需要精密时钟的相关装置具有极大的借鉴意义。

# 参考文献:

- [1] 李小群,党钊,陈骥,等. 一种单次精密时序电脉冲的产生方法[J]. 太赫兹科学与电子信息学报, 2007,5(2):126-129. (LI Xiaoqun,DANG Zhao,CHEN Ji,et al. Method of single low jitter timing electronic pulse sequence generation[J]. Journal of Terahertz Science and Electronic Information Technology, 2007,5(2):126-129.)

- [2] 高平,代刚,郭玉山,等. 多路纳秒延时同步脉冲的产生与传输[J]. 太赫兹科学与电子信息学报, 2007,5(2):123-125. (GAO Ping,DAI Gang,GUO Yushan,et al. Generation and transmission of multiplex nanosecond delay pulse[J]. Journal of Terahertz Science and Electronic Information Technology, 2007,5(2):123-125.)

- [3] 唐菱,陈骥,黄夏,等. ICF 同步触发信号传输的可靠性研究[J]. 太赫兹科学与电子信息学报, 2014,12(6):933-936. (TANG Ling,CHEN Ji,HUANG Xia,et al. Improving reliability of timing system in ICF driver based on FMECA method[J]. Journal of Terahertz Science and Electronic Information Technology, 2014,12(6):933-936.)

- [4] 周晓鹏,宋烨曦. 一种自适应低相位噪声相参时钟源的设计[J]. 太赫兹科学与电子信息学报, 2016,14(5):753-757. (ZHOU Xiaopeng,SONG Yexi. Design of an adaptive coherent clock source with low phase noise[J]. Journal of Terahertz Science and Electronic Information Technology, 2016,14(5):753-757.)

- [5] 董军,孙志红,卢宗贵. 基于级联光电的 ns 激光脉冲高对比度波形测量[J]. 太赫兹科学与电子信息学报, 2015,13(6): 971-975. (DONG Jun,SUN Zhihong,LU Zonggui. High-contrast measurement for ns high-power laser pulse based on cascaded photodetection[J]. Journal of Terahertz Science and Electronic Information Technology, 2015,13(6):971-975.)

- [6] 郑贵强. 锁相环路的宽带调频技术[J]. 太赫兹科学与电子信息学报, 2004,2(4):290-292. (ZHENG Guiqiang. Phase-locked loop broadband FM technology[J]. Journal of Terahertz Science and Electronic Information Technology, 2004,2(4): 290-292.)

- [7] 徐亮. 仿真分析在时钟电路电磁兼容设计中的应用[J]. 太赫兹科学与电子信息学报, 2009,7(3):202-205. (XU Liang. Application of simulation analysis in electromagnetic compatibility design of clock circuit[J]. Journal of Terahertz Science and Electronic Information Technology, 2009,7(3):202-205.)

- [8] ERIC Bogatin. Signal and power integrity:simplified[M]. Beijing:Publishing House of Electronics Industry, 2015.

- [9] Mercedes Casamayor. Application Note AN-715[EB/OL]. (2017-10-29). https://www.analog.com/media/cn/technical-documentation/application-notes/AN-715\_cn.pdf.

#### 作者简介:

刘亚迪(1995-), 女,河南省商丘市人,在读硕士研究生,主要从事激光器件相关电子电路研究.email:ydliu1004@163.com.

**王** 超(1983-), 男, 西安市人, 中级工, 主要从事高速快电子电路方面的研究.

**党 钊**(1970-),男,四川省射洪县人,研究员,主要从事高功率固体激光驱动器精密同步及控制技术研究.

**陈** 骥(1964-),男,湖南省湘乡市人,主要 从事高速快电子电路方面的研究.