Feb., 2012

INFORMATION AND ELECTRONIC ENGINEERING

文章编号: 1672-2892(2012)01-0068-05

## 基于双环X波段低相噪频率合成器的设计与实现

杨光1,杨杰1,蒋国琼2,宋烨曦1

(1.四川九洲电器集团有限责任公司,四川 绵阳 621000; 2.四川绵阳长虹股份有限公司,四川 绵阳 621000)

摘 要:基于相位噪声特性,对数字锁相式频率合成器进行了研究和分析。在对比传统单环锁相技术的基础上,介绍了一种双环技术的X波段低相噪锁相式频率合成器。在满足小频率步进、低杂散的情况下,设计所得到的X波段频率合成器其绝对相位噪声≤-100 dBc/Hz@1 kHz。

关键词: 低相位噪声; 双环技术; 锁相环

中图分类号: TN74<sup>+</sup>1

文献标识码: A

# Design and implementation of X-band low phase noise frequency synthesizer using dual-loop technology

YANG Guang<sup>1</sup>, YANG Jie<sup>1</sup>, JIANG Guo-qiong<sup>2</sup>, SONG Ye-xi<sup>1</sup> (1.Sichuan Jiuzhou Electric Group Co., Ltd., Mianyang Sichuan 621000, China; 2.Mianyang Sichuan Changhong Co., Ltd., Mianyang Sichuan 621000, China)

**Abstract:** The digital Phase Locked Loop(PLL) frequency synthesizer technology is researched and analysed based on phase noise performance. An X-band PLL frequency synthesizer based on dual loop technology is introduced in contrast to conventional single locked loop technique. This design features small frequency step and low spurious characteristics with phase noise below -100 dBc/Hz@1 kHz.

**Key words:** low phase noise; dual-loop technology; Phase Locked Loop

由于无线电通信和雷达技术的飞速发展,对系统性能提出了更高、更严格的要求,而系统性能主要的限制因素之一就是相位噪声<sup>[1]</sup>。相位噪声作为频率合成器最重要的技术指标,直接影响现代电子系统的性能,例如影响雷达的改善因子、接收机的检测能力、通信质量等<sup>[2]</sup>。微波频段,在满足频率合成器输出信号小步进、低杂散的要求下,要实现低相位噪声是相对困难的。本文采用双环技术实现的锁相式频率源,相对于传统的锁相式频率源,在低相位噪声特性方面具有更大优势,可同时满足系统对频率合成器的低相位噪声、小频率步进及低杂散等要求。

#### 1 传统锁相式频率合成器的相位噪声特性

传统的锁相式频率源是利用单环技术实现的间接数字锁相式频率合成器。间接数字锁相式频率合成器由数字锁相环构成,在锁相环内插入了数字分频器和数字鉴相器<sup>[2]</sup>。其简要原理如图1所示。

其输出信号频率的计算方法是:

$F_{\text{out}} = F_{\text{PD}} \times N \tag{1}$

$\begin{array}{c|c} F_{\text{PD}} & \text{Phase Detector} \\ \hline & (\text{PD}) & \text{loop filter} \end{array}$

Fig. 1 Schematic of indirect digital phase-locked frequency synthesizer

图 1 间接数字锁相式频率合成器简要原理框图

间接数字锁相式频率合成器具有体积小、成本低、频率步进小及便于集成等优点,但其输出相位噪声较差。间接数字锁相式频率合成器的输出信号相位噪声与锁相环内分频器的种类和分频次数有关,分频次数N越大,相位噪声越差。间接数字锁相式频率合成器的带内残留相位噪声计算方法为:

$PN_{\text{SYNTH}} = PN_{\text{TOT}} + 10 \lg F_{\text{PD}} + 20 \lg N$

式中: PN<sub>SYNTH</sub>为频率合成器的残留相位噪声; PN<sub>TOT</sub>为锁相环芯片底噪。

式中:  $F_{\text{out}}$ 为输出信号频率;  $F_{\text{PD}}$ 为鉴相器频率; N为频率合成器反馈分频比。

收稿日期: 2011-06-22; 修回日期: 2011-07-28

从式(1)及式(2)可见,在输出信号频率确定的情况下,间接数字锁相式频率合成器要获得低相位噪声,就必须降低反馈分频比N,提高鉴相频率 $F_{PD}$ 。理论上鉴相频率提高1倍,输出的相位噪声可以下降3 dB<sup>[3]</sup>。既提高鉴相频率,又可以满足小频率步进的一种方法,就是采用小数分频锁相环路(图1中N允许带小数),但小数分频锁相式频率合成器也存在一些问题,如离散相位调制边带<sup>[2]</sup>,难以满足低杂散的要求。此外,还有采用直接数字合成输出信号作为数字锁相式频率合成器参考信号的方法,但由于直接数字合成输出信号的带内杂散不甚理想,该类频率合成器也难以满足低杂散的要求。下文介绍另一种可同时获得小频率步进、低相位噪声的技术:采用双环技术的频率合成技术。

#### 2 基于双环的 X 波段低相噪锁相式频率合成器工作原理

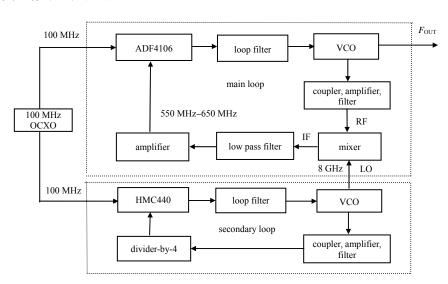

基于双环技术的频率合成器包括2个相关联的锁相环路。这2个相关联的锁相环路,一个锁相环路是独立的,它是一个辅助环路,其输出信号不直接输出,称之为副锁相环;另一个锁相环路产生频率合成器的输出信号,其反馈支路中通过混频方式插入了副锁相环的输出信号,称之为主锁相环。

副锁相环输出信号与主锁相环输出的反馈信号进行混频,混频后的信号经过滤波放大后送到主锁相环的锁相 环芯片,进行分频、鉴相后,实现主锁相环的锁相。主锁相环要实现锁相并获得期望的输出信号,其前提是副锁 相环已经处于锁定状态。

下面通过1个工程实例,介绍基于双环技术的X波段低相噪锁相式频率合成器的工作原理。该工程实例关键技术指标要求如下:

输出频率: 8 550 MHz~8 650 MHz(连续波);

频率步进: 2 MHz;

单边带相位噪声: ≤-95 dBc/Hz@1 kHz; ≤-100 dBc/Hz@10 kHz;

频率转换时间: ≤40 us;

杂散抑制: ≤-70 dBc;

谐波抑制: ≤-30 dBc;

输出功率: 10 dBm ± 1.5 dB;

从上面的指标可见,需要在X波段同时满足小频率步进、低相位噪声、低杂散和快速频率转换。本文采用基于双环的X波段锁相式频率合成技术,其工作原理如图2所示。

在该工程实例中,采用双环技术的目的是:副锁相环通过高鉴相频率获得8 GHz低相位噪声输出信号;副锁相环输出的8 GHz信号与主锁相环反馈信号混频,使主锁相环反馈到其锁相环芯片的频率降低至550 MHz~650 MHz,进而降低了主锁相环的反馈分频比,从而可以在满足小频率步进的情况下获得低相位噪声。

副锁相环的输出信号频率为8 GHz,采用的锁相环芯片是HITTITE公司的数字锁相环HMC440,鉴相频率取100 MHz,反馈分频比N=80(外置分频器分频比为4,HMC440数字分频比为20)。HMC440在其鉴相频率为100 MHz时,鉴相器底噪为-153 dBc/Hz

Fig.2 Schematic of X-band PLL frequency synthesizer with low phase noise using dual-loop technology

图 2 基于双环的 X 波段低相噪频率合成器简要原理框图

@10 kHz(即偏离载波10 kHz处 $PN_{TOT}$ +10lg  $F_{PD}$ =-153 dBc/Hz)。根据式(2),副锁相环能够获得的带内残留相位噪声是(离载波10 kHz处):  $PN_{SYNTH}$ =-153 dBc/Hz+20lg 80=-115 dBc/Hz。

主锁相环的输出频率为8 550 MHz~8 650 MHz,采用的锁相环芯片是AD公司的ADF4106,鉴相频率取2 MHz,

反馈到ADF4106的频率为550 MHz(ADF4106的射频输入频率需大于500 MHz),相应的反馈分频比 $N=275\sim325$ 。ADF4106的芯片底噪为-219 dBc/Hz。根据式(2),主锁相环能够获得的带内残留相位噪声为(不考虑混频对相位噪声的影响,反馈分频比按最高N=325计算):

PN<sub>SYNTH</sub>=-219 dBc/Hz+10lg (2×10<sup>6</sup>)+20lg 325=-108.5 dBc/Hz。这个结果与仿真结果基本一致,图3是通过AD公司仿真软件ADIsimPLL仿真的结果(环路带宽取200 kHz)。

Frequency Domain Analysis of PLL

Applying at PLL output forgumency of EEDMHz

因为混频器输出信号的相位噪声功率谱密度为2个输入信号相位噪声功率谱密度之和,所以副锁相环输出信号与主锁相环反馈信号混频后得到的中频信号相位噪声功率谱密度为两者之和。因此,该X波段频率合成器输出信号相位噪声要获得与图3仿真一致的结果,副锁相环输出的8 GHz信号的带内残留相位噪声要远优于主锁相环的带内残留相位噪声。采用的数字锁相环

| Frequency Domain Analysis of PLL Analysis at PLL output frequency of 650MHz |        |        |     |        |        |

|-----------------------------------------------------------------------------|--------|--------|-----|--------|--------|

| Phase Noise Table                                                           |        |        |     |        |        |

| Freq                                                                        | Total  | VCO    | Ref | Chip   | Filter |

| 100                                                                         | -104.3 | -163.1 |     | -104.3 | -180.1 |

| 1.00k                                                                       | -108.8 | -143.1 |     | -108.8 | -160.1 |

| 10.0k                                                                       | -109.4 | -123.2 |     | -109.6 | -140.2 |

| 100k                                                                        | -103.0 | -105.1 |     | -107.2 | -122.3 |

| 1.00M                                                                       | -118.8 | -119.2 |     | -130.1 | -141.2 |

Fig.3 Simulation results of phase noise within the main loop 图 3 主环环内相位噪声仿真结果

HMC440获得的8 GHz信号带内残留相位噪声为-115 dBc/Hz@10 kHz, 优于主锁相环的带内残留相位噪声约6 dB, 对主锁相环的实际带内残留相位噪声影响不大(恶化约1 dB)。

#### 3 电路设计与实现

#### 3.1 副锁相环的实现

副锁相环的锁相环芯片为HMC440QS16G, 其鉴相频率为10 MHz~1 300 MHz, 射频反馈可编程分频器的输入频率最高到2.8 GHz(可编程分频比为2~32)。在本工程实例中, 鉴相频率取100 MHz, 因射频反馈可编程分频器的输入频率最高只到2.8 GHz, 要实现8 GHz锁相, 就需要在射频反馈支路上嵌入1个外置分频器(本文选择的是/4分频器, HITTITE公司的HMC365S8G), 压控振荡器选择的是HITTITE公司的HMC506LP4(输出频率为7.8 GHz~8.8 GHz)。

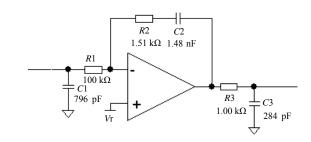

鉴相频率为100 MHz,在输出8 GHz信号中,离载波最近的杂散是由鉴相频率泄露引起的偏离载波±100 MHz处杂散。要使对该杂散信号的抑制度≤-70 dBc,就需要合理选择环路低通滤波器带宽,使鉴相频率泄露到压控振荡器频率调谐端的电平足够低。根据需要,选择的环路带宽为1 MHz,其环路滤波器相关电路模型如图4所示。此外,因射频反馈支路需经过除4分频,为降低分频后信号泄露到输出信号端所产生的杂散电平(如除4分频产生的2 GHz与输出信号进行混频产生6 GHz及10 GHz杂散信号),需要在副锁相环的射频反馈支路采取耦合、衰减、高通滤波及放大等处理。经过处理后,可将副锁相环输出端与其射频反馈端的隔离度提高到70 dB以上,进而保证副锁相环输出8 GHz的杂散抑制信号。

#### PLL Schem Input Reference Phase Noise VCO Phase Noise Results Ra Ra 士点 Rb Rn HHII± ca Φ Margin 45.00 deg Loop Band: 200.0E3 - Ω Opamp Eq. ... 800.0E-12 V/rt Hz 100.00 Rb: 66.6668E0 6.55538481E-9 F 28.9802727E-9 F View Filter

Fig.4 Associated circuit model of vice PLL loop filter 图 4 副锁相环环路滤波器相关电路模型

#### 3.2 主锁相环的实现

主锁相环选择压控振荡器时因注意其输出频率范围,如果选择不当,则可能出现频率错锁。该工程实例中,主锁相环的反馈信号与8 GHz固定信号混频产生中频信号时,主锁相环输出反馈信号高于或低于8 GHz时都可得到要求的中频信号。即主锁相环输出信号在8 550 MHz~8 650 MHz或7 350 MHz~7 450 MHz,该双环频率合成器都可以锁定。为了避免频率错锁,主锁相环就需要选择工作频率高于7 450 MHz的压控振荡器,比如选择工作频率为8 GHz~9 GHz的压控振荡器。

主锁相环的锁相环芯片为AD公司的ADF4106BRU,如果压控振荡器对应输出频率的最高调谐电压超过+5 V,就需要选择有源环路滤波器。根据关键技术指标(频率步进为2 MHz)的要求,鉴相频率取2 MHz。因此,偏离载波最近的杂散信号,是由鉴相频率泄露引起的偏离载波±2 MHz处杂散,综合考虑关键技术指标要求(频率转换时间≤40 μs),环路带宽取200 kHz(环路带宽最大不能超过鉴相频率的1/5,否则会大幅增加环路的不稳

定性)。主锁相环的环路滤波器电路模型如图5所示(压控振荡器的调谐灵敏度按50 MHz/V计算)。

同副锁相环类似,主锁相环压控振荡器的输出端和射 频反馈支路间需要采取耦合、衰减及放大等处理,提高其 隔离度,改善杂散抑制。

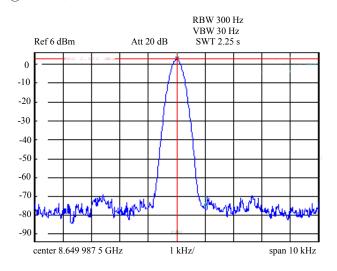

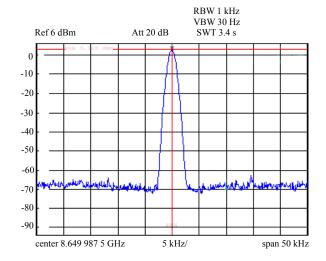

### 4 测试结果

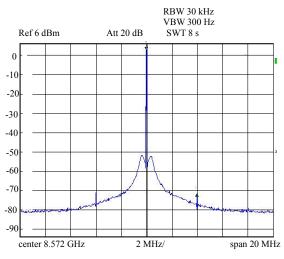

本文设计的基于双环技术的X波段低相噪锁相式频率 合成器,其输出信号单边带相位噪声测试结果如图6所示,

Fig.5 Circuit model of the main PLL loop filter 图 5 主锁相环环路滤波器电路模型

输出信号频谱测试结果如图7所示。测试结果表明,输出信号单边带相位噪声: $\leq 100 \text{ dBc/Hz}$ @1 kHz, $\leq -100 \text{ dBc/Hz}$  @10 kHz;杂散抑制 $\leq -74 \text{ dBc}$ 。

Fig.6 Testing results of SSB phase noise 图 6 单边带相位噪声测试结果

Fig.7 Frequency spectrum of output signal 图 7 输出信号频谱

注:该测试结果是在100 MHz,参考晶振相位噪声 ≤ -145 dBc/Hz@1 kHz, ≤ -150 dBc/Hz@10 kHz的情况下测试得到的单边带相位噪声。由于缺乏信号源分析仪等高端相噪测试仪器,该X波段频率合成器的相位噪声结果由频谱分析仪测试获得,根据前面的分析,其实际相位噪声应优于用频谱分析仪获得的测试结果。

(下转第81页)