Vol. 10, No. 1 Feb., 2012

文章编号: 1672-2892(2012)01-0077-05

2012年2月

# 基于 AD9910 的多通道信号发生器

胡茂海, 蒋鸿宇, 严 俊, 文 豪, 富艳琴

(中国工程物理研究院 电子工程研究所,四川 绵阳 621900)

要:基于直接数字频率合成(DDS)技术,采用现场可编程门阵列(FPGA),通过对 DDS 芯片 AD9910 的控制,实现多通道信号发生器的设计。所设计的信号发生器具有高频率精度、低杂散、 捷变频的特点,并可编程调整输出频率值以及多路输出信号之间的相位值。实测结果表明,本文 所研究的方法和研制的系统是可行、有效的, 具有广阔的应用前景。

关键词:直接数字合成;现场可编程门阵列;多通道信号发生器

中图分类号: TN47

文献标识码: A

## Multi-channel signal generator based on AD9910

HU Mao-hai, JIANG Hong-yu, YAN Jun, WEN Hao, FU Yan-qin (Institute of Electronic Engineering, China Academy of Engineering Physics, Mianyang Sichuan 621900, China)

Abstract: As the development of multicarrier communication technology, multi-channel signal generator has become more and more important. Based on the Direct Data Synthesis(DDS) technology, this design uses FPGA to control the AD9910 to implement a kind of multi-channel signal generator. This multi-channel signal generator features high frequency precision, low stray, fast frequency switching, and programmable adjustment of the multi-phase value of the output signal. Measured results show that this method is feasible and effective, and it would be widely applied in the future.

Key words: Direct Digital Synthesis; FPGA; multi-channel signal generator

在现代雷达、通信和电子对抗领域中、信号发生器得到广泛应用、同时对信号的指标要求也越来越高。在目 前信号频率合成的各种类型中,直接数字频率合成(DDS)[1]技术是近年来迅速发展起来的频率合成方法。DDS采 用数字存储技术,通过相位累加、幅度查表以及数模变换来实现波形产生,因具有超宽的相对带宽,超高的频率 捷变速度,超细的频率分辨力,相位连续,全数字化,便于单片集成等优越性能而得到广泛应用[2]。本文介绍了 一种基于DDS技术实现的高频率分辨力、低杂散、捷变频的多通道信号发生器设计方案。

#### DDS 调制原理

DDS是一种理想的调制器,因为合成信号的3个参量: 频率、相位和幅度均可由数字信号精确控制,因此DDS 可以通过预置相位累加器的初始值来精确控制合成信号的相位,从而达到调制的目的。

DDS的理论依据是时域抽样定理,即一个频带限制在 $0 \sim f_c/2$ 范围内的时间信号f(t),如果以 $T_c = 1/f_c$ 的时间 间隔对它进行等间隔抽样,则信号完全由得到的抽样值确定,即该信号f(t)可以由其采样值完全恢复。DDS正是 基于此原理,将一个阶梯化的信号(采样信号)通过一个理想的低通滤波器,以得到原始的连续信号。

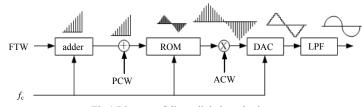

DDS的基本原理<sup>[3-5]</sup>如图1所示,它主要由5个部分组成:相位累加器、正弦查询表、数模转换器、低通滤波 器和参考时钟。DDS工作时,通过改变相位累加器的频率控制字(Frequency Tune Word, FTW)来改变相位增量, 相位增量的不同,将导致一周内的取样点数不同。取样是在系统时钟控制下进行的,即取样周期是一定的,根据 相位增量的不同,从ROM中读取的信号周期就不同。ROM输出的二进制数送到DAC进行D/A变换,得到模拟形 式量化(阶梯式)的正弦波。最后经过滤波器滤除不需要的频率分量,平滑得到正弦波,输出正弦波的频率为:

收稿日期: 2011-01-03; 修回日期: 2011-04-11

$$f_{\text{out}} = \frac{FTW}{2^N} \times f_{\text{c}} \tag{1}$$

为了达到足够小的频率分辨力,通常将相位累加器的位数N取大,如N=32。但受体积和成本的限制,即使采用先进的存储方式,ROM的容量都远小于此,因此在对ROM寻址时,只是用相位累加器的部分高位去寻址,这样不可避免地引进误差,即相位截断误差。

Fig.1 Diagram of direct digital synthesizer 图1 DDS原理框图

另外,一个幅值在理论上只能用一个无限长的二进制代码才能精确表示,由于ROM的存储能力,只采用一定比特代码来表示这一幅值,这必然会引起幅度量化误差。另外,DAC的有限分辨力以及非线性也会引起误差。因此,DDS杂散是DDS本身所固有的,主要由相位舍位、幅度量化和DAC的非理想特性所引起。

#### 2 芯片选择

应某多载波通信系统要求,信号发生器需要同时输出最大10路信号,每路信号的频率、幅度、初始相位均单独可调,它们之间可实现任意相位差要求,且要求输出的信号具有高分辨力、低杂散、快速捷变频等特点。

基于以上要求,设计采用ADI公司的DDS芯片AD9910<sup>[6]</sup>,该芯片无杂散动态范围达到80 dBc,相位噪声达到140 dBc/Hz。由于采样频率 $f_{SYSCLK}$ 达到1 GSPS<sup>[7]</sup>,内部相位累加器为32 bit(即将2 $\pi$ 分为2<sup>32</sup>等份),即频率分辨力 $\Delta f$ 可以达到 $\Delta f = f_{SYSCLK}/2^{32} \approx 0.23$  Hz;相位偏移控制字(Phase Offset Word,POW)为16 bit,可方便地实现输出波形的初相角 $\phi$ 的调制( $\phi = 2\pi \times POW/2^{16}$ );内部D/A为14 bit,主时钟 $f_{SYSCLK}$ 最高为1 GHz,输出信号频率最高可达400 MHz。另外,除可产生正弦波外,AD9910还可以通过内部寄存器配置,输出FKS,PSK,ASK信号及周期的任意波信号。AD9910的并口调制模式提供了更新速率可达250 MHz 的16 bit 快速编程的并行接口,使每隔8 ns更新1次32 bit的频率控制字成为可能,这种快速编程能力可以满足系统捷变频的要求。

### 3 系统设计

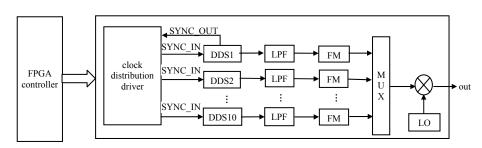

系统电路由FPGA控制单元、AD9910信号发生单元、时钟分配单元、合路及变频单元组成。根据系统提出的要求,FPGA控制单元将输出信号的形式、初始相位、频率、幅度等控制信息发送给信号发生单元和时钟分配单元,使其产生最大10通道的同步信号,每通道信号经滤波、倍频(Frequency Multiplier, FM)、放大后送给合路器合成1路信号,再经变频器上变频到合适的频率输出,系统原理框图如图2所示。

Fig.2 Block diagram of multi-channel signal generator 图 2 多通道信号发生器结构框图

对于DDS来讲,捷变频速度取决于控制字写入的速度和系统时钟的速率。为提高控制字写入的速度,系统控制单元采用XILINX公司的V5芯片来实现。V5芯片集成了大量的I/O接口,且处理速度高达500 MHz,能同时完成10通道DDS的捷变频控制。

AD9910信号发生单元采用ADI公司的DDS芯片AD9910,采样时钟为1 GHz。每通道信号发生单元通过接收FPGA控制器的控制字产生相应的信号输出,经低通滤波后送给合路器。

时钟分配单元的作用是实现多通道信号发生单元的同步工作。要实现多通道同步,就必须满足3个条件:多通道DDS工作在相关的工作时钟之下;多通道DDS有相关的同步时钟;在每片DDS内部作一定的时延设定,使同步时钟信号与工作时钟之间满足确定的采样关系。因此,系统设计将1路1 GHz时钟信号功分为10路时钟信号,

送给10个信号发生单元作采样时钟, 使其满足第1个条件。以第1路DDS 的同步时钟输出信号(SYNC OUT)作为时钟分配器的输入,输出10路相关 的同步时钟信号,连接到10路DDS芯片作同步时钟输入(SYNC IN),实现 第2个条件。通过FPGA控制器控制每通道同步时钟输入信号的时间延迟, 以确保满足合适的采样关系,从而实现多通道信号发生单元间的同步。

合路及变频单元完成多通道信号的滤波、倍频、放大、多通道信号 合成及上变频功能,以最终实现在较高频率的多载波信号输出。

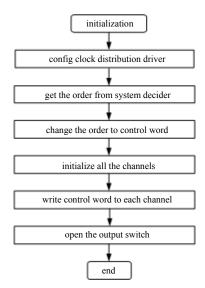

系统工作首先是对各个单元进行初始化和复位,接着配置时钟分配 单元, 使10通道信号发生单元同步工作, 然后等待系统命令, 根据任务 要求读取各通道的信号形式、频率、相位、幅度信息,对系统命令作进 一步的解析(选通的通道个数,具体选通的是哪几个通道等),并计算相应 的控制字。在下发新的指令之前,需要初始化所有通道信号,关断合路 信号输出,确保新命令的准确执行。FPGA控制器根据系统命令,下发控 制字给所有通道,控制信号发生单元输出多通道信号。最后打开合路输 出开关,输出合路信号,具体程序控制流程如图3所示。

10通道信号的相位控制是通过FPGA控制器计算得出。通过峰均比抑 制算法, 计算得出峰均比最小的相位组合, 进而控制10通道的相位, 部 分代码如下:

begin

```

always @(posedge FJB_CLK)

if (!FJB RESTM)

begin

z < = 0;

maxi <= 0;

min<=16'hffff;

muo \le NN*16'h0800;

phaseq0<=16'h0000;phaseq1<=16'h0100;phaseq2<=16'h0200;

phaseq3<=16'h0300;phaseq4<=16'h0400;phaseq5<=16'h0500;

phaseq6<=16'h0600;phaseq7<=16'h0700;phaseq8<=16'h0800;

phaseq9<=16'h0900;

end

else

begin

if(y10<muo)

z \le muo-y10;

z \le y10-muo;

else

if(z>maxi)

\max_{i \le z};

if(set130 == 1)

begin

if(maxi<min)

begin

min<=maxi;

case(counter10)

phaseq0<=phase[0];

4'b0000:

phaseq1<=phase[1];

4'b0001:

phaseq2<=phase[2];

4'b0010:

4'b0011:

phaseq3<=phase[3];

phaseq4<=phase[4];

4'b0100:

phaseq5<=phase[5];

4'b0101:

4'b0110:

phaseq6<=phase[6];

phaseq7<=phase[7];

4'b0111:

phaseq8<=phase[8];

4'b1000:

4'b1001:

phaseq9<=phase[9];

default:

begin

phaseq0<=16'h0000;phaseq1<=16'h0100;phaseq2<=16'h0200;

phaseq3<=16'h0300;phaseq4<=16'h0400;phaseq5<=16'h0500;

```

phaseq6<=16'h0600;phaseq7<=16'h0700;phaseq8<=16'h0800;

Fig.3 Software flowchart 图 3 软件流程图

```

phaseq9<=16'h0900;

end

endcase

end

maxi<=0;

if(set10==1) min<=16'hffff;

end

end

```

## 4 测试结果

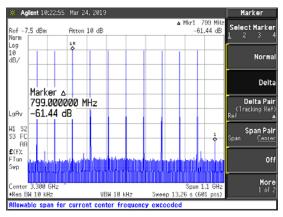

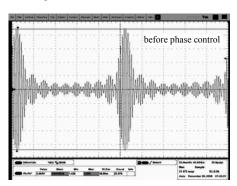

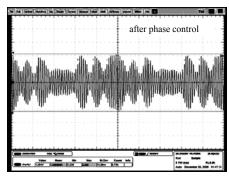

本文设计的多通道信号发生器,其特性在实验上得到了证明,即测试结果完全满足设计要求。以输出10通道信号为例,合路信号具有低杂散、相位噪声良好的特性。图4为用Agilent频谱仪测量的10通道合路信号输出频谱图,图5为用Tek示波器测量的相位精确控制前、后的10通道合路信号时域波形图。

Fig.4 Spectrum of output signal 图 4 十通道合路信号频域图

根据实际测试结果,基于 AD9910 的多通道信号发生器能同时产生最多 10 路信号,信号杂散-60 dB,每路信号最大功率-3 dBm;通过精确控制每通道信号的初始相位,可以有效降低合路信号的峰均比值,峰均比抑制能力最大可达 6 dB<sup>[8]</sup>。

Fig. 5 Time domain waveform of output signal 图 5 十通道合路信号时域图

#### 5 结论

随着数字技术的不断发展,直接数字式频率合成器技术将会得到不断的完善。本文以 FPGA 控制器为核心,利用当前使用广泛的 DDS 技术,可输出高分辨力、低杂散、捷变频的多通道信号,配置灵活、方便,结构清晰,若需满足其他频段信号的一些特殊要求,只需改变一些电路参数及控制电路的软件即可,可用于各种多载波通信系统。

#### 参考文献:

- [1] Tierney J,Rader C,Gold B. A Digital Frequency Synthesizer[J]. IEEE Transactions on Audio and Electroacoustics, 1971,19(1): 48-57.

- [2] 潘松,黄继业. EDA 技术与 VHDL[M]. 北京:清华大学出版社, 2005. (PAN Song, HUANG Jiye. EDA technology and VHDL[M]. Beijing:Tsinghua University Press, 2005.

- [3] Bonfanti A,Amorosa F,Samori C,et al. A DDS-Based PLL for 2.4-GHz Frequency Synthesis[J]. IEEE Trans. on Circuits and Systems, 2003,50(12):1007-1010.

- [4] 许慧波,张厥胜. DDS-直接数字式频率合成器综述[M]. 西安:西安电子科技大学出版社, 1989. (XU Huibo,ZHANG Juesheng. Review of Direct Digital Synthesizer[M]. Xi'an: Xidian University Press,1989.

- [5] Jin Fengjie. Use of DSP and DDS technique in radar signal generator[C]// Proceeding ICSP'04. Beijing:[s.n.], 2004,3: 1950-1952.

- [6] Analog Devices. AD9910 datasheet[R]. 2007.

- [7] 徐晓东,王西锋. 基于高速 DDS 芯片的宽带低杂散信号产生器的设计与实现[J]. 雷达与对抗, 2007(4):32-35. (XU Xiaodong,WANG Xifeng. The design and implementation of a fast DDS chip based wide-band,low-stray signal generator[J]. Radar & Ecm, 2007(4):32-35.

- [8] 胡茂海,叶江峰,严俊,等. 基于 FPGA 的实时峰均比抑制算法[J]. 信息与电子工程, 2010,8(5):565-568,593. (HU Mao hai,YE Jiangfeng,YAN Jun,et al. A Realtime PAPR Reduction Algorithm Based on FPGA[J]. Information and Electronic Engineering, 2010,8(5):565-568,593.)

#### 作者简介:

胡茂海(1982-), 男, 四川省遂宁市人, 研究实习员, 主要从事数字信号处理研究工作。email:humaohai2001@sina.com。

**文** 豪(1982-), 男,四川省绵阳市人,助理研究员,主要从事数字信号处理研究工作.

**蒋鸿宇**(1982-),男,四川省绵阳市人,在读博士研究生,主要从事高速率数字采集、通信信号处理相关研究.

**严 俊**(1981-), 男, 四川省绵阳市人, 研究 实习员, 主要从事数字信号处理研究工作.

**富艳琴**(1984-), 女, 甘肃省武威市人, 研究 实习员, 主要从事数字信号处理研究工作.

(上接第71页)

#### 5 结论

本文介绍的基于双环X波段低相噪锁相式频率合成器技术,在满足小频率步进、低杂散的情况下,绝对相位噪声达到≤-100 dBc/Hz@1 kHz。其双环技术具有一定先进性与通用性,该技术实现的频率合成器可以满足系统对高质量信号源的要求,具有广阔的应用前景。

#### 参考文献:

- [1] 白居宪. 低噪声频率合成[D]. 西安:西安交通大学, 1995.

- [2] 高树亭,高峰,徐盛旺,等. 合成频率源工程分析与设计[M]. 北京:兵器工业出版社, 2008.

- [3] 万天才. 频率合成器技术发展动态[J]. 微电子学, 2004,34(4):366-370.

#### 作者简介:

**杨** 光(1976-),男,四川省遂宁市人,硕士,研究方向为频率合成器及相关产品.

**杨** 杰(1969-),男,四川省绵阳市人,本科,研究方向为微波技术.

**蒋国琼**(1978-),女,四川省广安市人,本科,研究方向为数字信号处理.email:guoqiong.jiang@changhong.com.

宋烨曦(1985-), 男,四川省乐山市人,硕士,研究方向为频率合成器及相关产品.